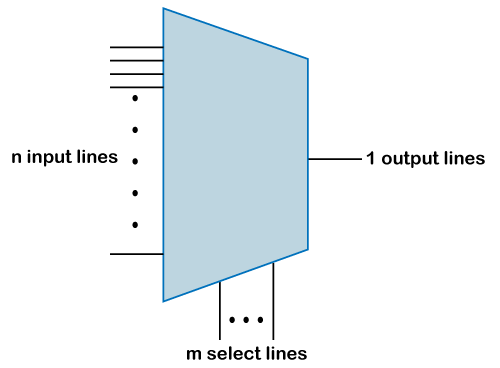

- System verilog for parallel to serial converter code#

- System verilog for parallel to serial converter free#

System verilog for parallel to serial converter code#

Sur la vidéo DÉMO : Switch Controls sur sortie VGA et Picture Loading and VGA Flash Code transfert sur écran LCD monté sur le Board. Logic Gates webpage: eng_circuitos_tut22.php

System verilog for parallel to serial converter free#

Then downlaod the free licence softwares. (software free for students) Create an account using real + fake data if you want. Stay tuned for more of this ROAD TO FPGAs series. Now, let't take a quick introductiion to Verilog.

Thanks to JLCPCB for supporting this video. But it doesn't translate well to today's engineering environment.īest & Fast Prototype ($2 for 10 PCBs): 🤍 I guess that's because Verilog was designed as an interpretive language. This makes it ideal when you have multiple design projects. VHDL uses libraries to store entities, architectures and configurations. Verilog needs functions and procedures put in different file systems to be used again. Which one lets me recycle files and minimize re-inventing the wheel or circular circuit? Change the order of the files and you can get very different results.Ī lot of the hassle can be made up for by code re-use. Using Verilog means you have to be careful how you compile it. Verilog data types are a lot simpler, if limited. It feels like you can learn Verilog faster because you can get going, but you don't find the error later until you're in the simulation phase. Which one is easier to use? I've heard Verilog is easier because it has fewer roles. Then again, it gives you a steep learning curve because it is not as intuitive. VHDL is not like C, which for a lot of people is a plus. Verilog sometimes only does as good a job at modeling as VHDL when using PLI too. Verilog is probably easier to learn, assuming you don't need to learn PLI. Whereas JavaScript frameworks showed up in 20, and a 12 month head start is a big deal. That's not a big difference when you consider it was 30 years ago. VHDL came out in 1987, while Verilog goes back to 1983. Verilog has been used a lot longer than VHDL.

They are both industry standard hardware description languages.Īt least there is only one TLA in that sentence. They are both perfectly good HDLs for programming and modeling FPGA.

0 kommentar(er)

0 kommentar(er)